目录

产品概述 返回TOPJ8G嘉泰姆

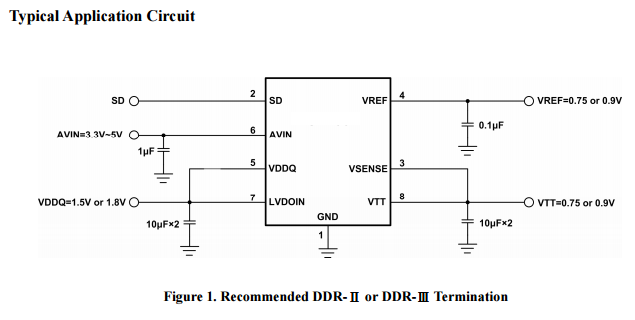

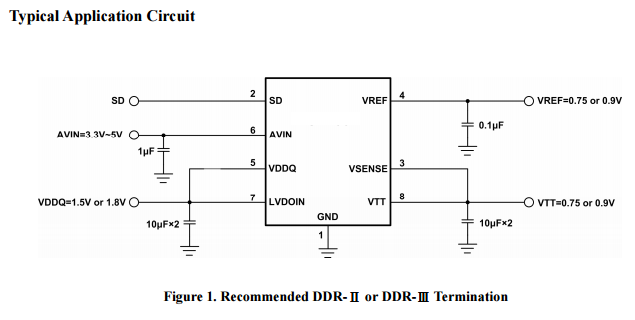

CXTP65156是一款为DDR内存总线的终端提供电源而专门设计的高性能线性稳压器,同以往开关型解决方案相比,它大大减少了外围器件的个数和占用的PCB空间,并降低了系统的整体成本。CXTP65156的高速运算放大器对负载具有快速优良的瞬态响应,CXTP65156还采用了VSENSE pin以达到优越的负载调整率;CXTP65156采用VREF输出为chipset和DIMMs提供基准电压。CXTP65156的另外一个特点是设计了低电压有效关断pin SD,当SD被拉低时,VTT的输出将处于高阻状态;但VREF依然保持在有效状态,在这种状态下,芯片因为其低的静态电流而功耗减小。CXTP65156利用与串联终端电阻连接的方式为高速传输线的有源终端结构提供优良的电压源。The CXTP65156 is a high performance linear regulator

designed to provide power for termination of a DDR

memory bus. It significantly reduces parts count,

board space and overall system cost over previous

switching solutions.

The CXTP65156 contains a high-speed operational

amplifier to provide excellent response to load

transients. The CXTP65156 also incorporates a VSENSE

pin to provide superior load regulation and a VREF

output as a reference for chipset and DIMMs.

An additional feature found on the CXTP65156 is an

active low shutdown (SD ) pin. When SD is pulled

low the VTT output will Tri-state providing a high

impedance output, but, VREF will remain active. A

power savings advantage can be obtained in this mode

through lower quiescent current.

The CXTP65156, used in conjunction with series

termination resistors, provides an excellent voltage

source for active termination schemes of high speed

transmission lines as those seen in high speed memory

buses.

产品特点 返回TOPJ8G嘉泰姆

J8G嘉泰姆

•输入电源电压(AVIN):3.15V~5.5VJ8G嘉泰姆

•VLDOIN电源输入范围:1.5V~3.3VJ8G嘉泰姆

•快速瞬态响应</p>

•DDR-Ⅱ和DDR-Ⅲ的终端电压:</p>

•可稳定提供/吸收1.5A电流J8G嘉泰姆

•低电流关断模式</p>

•过温保护功能J8G嘉泰姆

•全负载高精度输出电压J8G嘉泰姆

•外围器件少</p>

•SOP_8封装J8G嘉泰姆

•符合RoHS规范,100%无铅及Pb-Free 和Halogen-FreeJ8G嘉泰姆

� Input Voltage Range (AVIN): 3.15V to 5.5VJ8G嘉泰姆

� VLDOIN Voltage Range : 1.5V to 3.3VJ8G嘉泰姆

� Fast Transient Response TimeJ8G嘉泰姆

� Support DDRⅡ and DDRⅡ Requirements:

Source/Sink 1.5A for DDRⅡ</p>

Source/Sink 1.5A for DDRⅡ</p>

� Low-Current Shutdown ModeJ8G嘉泰姆

� Over-Temperature ProtectionJ8G嘉泰姆

� High Accuracy Output Voltage at Full-LoadJ8G嘉泰姆

� Low External Component CountJ8G嘉泰姆

� Available in SOP-8 (EP) PackageJ8G嘉泰姆

� RoHS Compliant and 100% Lead (Pb)-Free

Halogen-Free

J8G嘉泰姆

应用范围 返回TOPJ8G嘉泰姆

J8G嘉泰姆

•可为DDR-Ⅱ和DDR-Ⅲ提供终端电压� J8G嘉泰姆

DDR-Ⅱ and DDR-Ⅱ termination voltageJ8G嘉泰姆

技术规格书(产品PDF) 返回TOP J8G嘉泰姆

需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持</span>!</span>

J8G嘉泰姆

J8G嘉泰姆

J8G嘉泰姆

产品封装图 返回TOPJ8G嘉泰姆

aJ8G嘉泰姆

电路原理图 返回TOPJ8G嘉泰姆

J8G嘉泰姆

J8G嘉泰姆

J8G嘉泰姆

DDR终端稳压器</span>J8G嘉泰姆 |

Part NumberJ8G嘉泰姆 | remarkJ8G嘉泰姆 | Iout (A)J8G嘉泰姆 | Vin (V)J8G嘉泰姆 | Vout (V)J8G嘉泰姆 | Output Voltage Accuracy (mV)J8G嘉泰姆 | ShutdownJ8G嘉泰姆 | PackageJ8G嘉泰姆 |

CXTP65153J8G嘉泰姆 | 1.5A DDR Termination RegulatorJ8G嘉泰姆 | ± 1.5J8G嘉泰姆 | 1.8 ~ 5.5J8G嘉泰姆 | 0.9~1.25J8G嘉泰姆 | ± 20J8G嘉泰姆 | YesJ8G嘉泰姆 | SOP-8 (EP)J8G嘉泰姆 |

CXTP65154J8G嘉泰姆 | 2A Sink/Source Bus Termination RegulatorJ8G嘉泰姆 | ± 2J8G嘉泰姆 | 1.8 ~ 5.5J8G嘉泰姆 | 0.9~1.25J8G嘉泰姆 | ± 20J8G嘉泰姆 | YesJ8G嘉泰姆 | SOP-8 (EP)J8G嘉泰姆 |

CXTP65155J8G嘉泰姆 | Sink/Source DDR Termination RegulatorJ8G嘉泰姆 | ± 2J8G嘉泰姆 | 2.375 ~ 5.5J8G嘉泰姆 | 0.5~1.8J8G嘉泰姆 | ± 25J8G嘉泰姆 | YesJ8G嘉泰姆 | TDFN-10,SOP-8J8G嘉泰姆 |

CXTP65156J8G嘉泰姆 | DDR Termination RegulatorJ8G嘉泰姆 | ± 1.5J8G嘉泰姆 | 1.5~3.3J8G嘉泰姆 | 0.75~0.9J8G嘉泰姆 | ±20J8G嘉泰姆 | YesJ8G嘉泰姆 | SOP-8(EP)J8G嘉泰姆 |

J8G嘉泰姆

中文

中文 English

English

发表评论