目录

产品概述 返回TOPf1D嘉泰姆

The CXLC8974 consists of 14+1 channel buffers target

toward the needs of thin film transistor liquid crystal

display (TFT LCD). This device incorporates one

Vcom buffer and 14 gamma buffers, and are programmed

through I2

C interface. It contains two register

banks which can store two different sets of gamma

reference values. Each buffer is capable of driving

heavy capacitive loads and offering large current loading

(Vcom: 100mA, Gammas: 25mA).

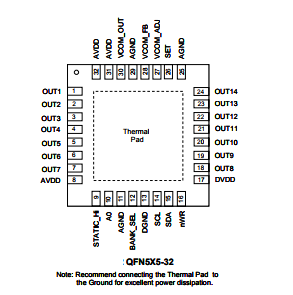

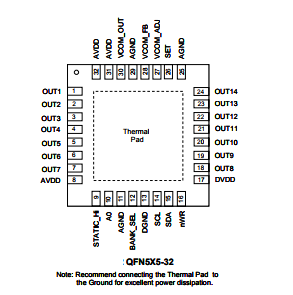

The CXLC8974 is available in the QFN5X5-32 package

产品特点 返回TOPf1D嘉泰姆

„ Supply Operation Range : 6.5V to 18V f1D嘉泰姆

„ 14+1 Channels : f1D嘉泰姆

--- 14 Channel Rail-to-Rail Programmable

Gamma Buffers f1D嘉泰姆

Š 10 bits Resolution for each Channel f1D嘉泰姆

Š 25mA Output Current for each Channel f1D嘉泰姆

Š 2 Banks Registers Using Bank_Sel to Select

which Bank Data Output f1D嘉泰姆

---1 Channel Rail-to-Rail Vcom Buffer: f1D嘉泰姆

Š 7 Bits Adjustable Output f1D嘉泰姆

Š ±100mA Output Current f1D嘉泰姆

Š ±260mA Output Short-Circuit Current f1D嘉泰姆

Š 20V/μs Slew Rate f1D嘉泰姆

„ 2-Wire I2

C Slave Mode Interface f1D嘉泰姆

„ Using One Control Pin Enable to Store Data into

Non-Volatile Memory (NVM) f1D嘉泰姆

„ Non-Volatile Memory (NVM) Store Setting (at

Least 100 Re-Write Times) f1D嘉泰姆

„ QFN5X5-32 Packagef1D嘉泰姆

应用范围 返回TOPf1D嘉泰姆

„ TFT-LCD Monitors f1D嘉泰姆

„ LCD Televisionsf1D嘉泰姆

技术规格书(产品PDF) 返回TOP f1D嘉泰姆

需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持</span>!</span>

f1D嘉泰姆

f1D嘉泰姆

f1D嘉泰姆

产品封装图 返回TOPf1D嘉泰姆

f1D嘉泰姆

f1D嘉泰姆

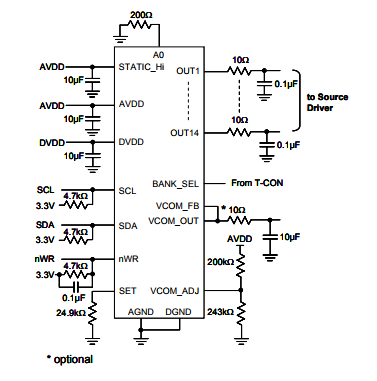

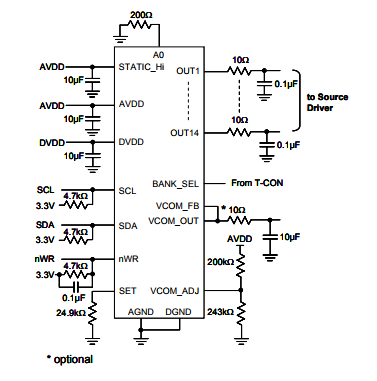

电路原理图 返回TOPf1D嘉泰姆

f1D嘉泰姆

f1D嘉泰姆

f1D嘉泰姆

ntegrated Bufferf1D嘉泰姆 |

Part NO.f1D嘉泰姆 | VDDf1D嘉泰姆 (V)f1D嘉泰姆 minf1D嘉泰姆 | VDD f1D嘉泰姆 (V)f1D嘉泰姆 maxf1D嘉泰姆 | CH f1D嘉泰姆 Vr+f1D嘉泰姆 Vcomf1D嘉泰姆 | IOUTf1D嘉泰姆 (mA) f1D嘉泰姆 Vr,Vcomf1D嘉泰姆 | S/R f1D嘉泰姆 (V/μs)</span>f1D嘉泰姆 Vr,Vcomf1D嘉泰姆 | BW (MHz)</span>f1D嘉泰姆 Vr,Vcomf1D嘉泰姆 | ISC (mA)f1D嘉泰姆 Vr,Vcomf1D嘉泰姆 | Notef1D嘉泰姆 | Packagef1D嘉泰姆 |

CXLC8973f1D嘉泰姆 | 6.5f1D嘉泰姆 | 18f1D嘉泰姆 | 1f1D嘉泰姆 | 100f1D嘉泰姆 | 20f1D嘉泰姆 | 19f1D嘉泰姆 | 260f1D嘉泰姆 | SMBus, Rail-to-Rail Outputf1D嘉泰姆 | TDFN3X3-10f1D嘉泰姆 |

CXLC8974f1D嘉泰姆 | 9f1D嘉泰姆 | 20f1D嘉泰姆 | 14+1f1D嘉泰姆 | 25, 100f1D嘉泰姆 | 16, 70f1D嘉泰姆 | 10, 19f1D嘉泰姆 | 100, 260f1D嘉泰姆 | Rail-to-Rail Output, f1D嘉泰姆 SMBus,2 Banks MTPf1D嘉泰姆 | QFN5X5-32f1D嘉泰姆 |

CXLC8975f1D嘉泰姆 | 6.5f1D嘉泰姆 | 19.5f1D嘉泰姆 | 18+1f1D嘉泰姆 | 30, 100f1D嘉泰姆 | 16, 80f1D嘉泰姆 | 9, 15f1D嘉泰姆 | 120, 300f1D嘉泰姆 | Rail-to-Rail Outputf1D嘉泰姆 | TQFP7X7-48/(FD)f1D嘉泰姆 |

CXLC8976f1D嘉泰姆 | 6.5f1D嘉泰姆 | 19.5f1D嘉泰姆 | 14+1f1D嘉泰姆 | 30, 100f1D嘉泰姆 | 16, 80f1D嘉泰姆 | 9, 15f1D嘉泰姆 | 120, 300f1D嘉泰姆 | Rail-to-Rail Outputf1D嘉泰姆 | TQFP7X7-48/(FD)f1D嘉泰姆 |

CXLC8977f1D嘉泰姆 | 7f1D嘉泰姆 | 20f1D嘉泰姆 | 12+1f1D嘉泰姆 | 25, 100f1D嘉泰姆 | 16, 50f1D嘉泰姆 | 30f1D嘉泰姆 | 100, 300f1D嘉泰姆 | Rail-to-Rail Output, f1D嘉泰姆 SMBus,2 Banks REGf1D嘉泰姆 | QFN4X4-24f1D嘉泰姆 |

CXLC8978f1D嘉泰姆 | 7f1D嘉泰姆 | 20f1D嘉泰姆 | 16+2f1D嘉泰姆 | 25, 100f1D嘉泰姆 | 16, 50f1D嘉泰姆 | 30f1D嘉泰姆 | 100, 300f1D嘉泰姆 | Rail-to-Rail Output,f1D嘉泰姆 SMBus,2 Banks MTPf1D嘉泰姆 | QFN5X5-28f1D嘉泰姆 |

CXLC8979f1D嘉泰姆 | 7f1D嘉泰姆 | 20f1D嘉泰姆 | 12+1+1f1D嘉泰姆 | 25, 100f1D嘉泰姆 | 16, 50f1D嘉泰姆 | 30f1D嘉泰姆 | 100, 300f1D嘉泰姆 | Rail-to-Rail Output, SMBus,Banks MTP, CRCf1D嘉泰姆 | QFN4X4-24f1D嘉泰姆 |

CXLC8980f1D嘉泰姆 | 6.5f1D嘉泰姆 | 18f1D嘉泰姆 | 14+1f1D嘉泰姆 | 25, 100f1D嘉泰姆 | 20, 20f1D嘉泰姆 | 10, 20f1D嘉泰姆 | 75, 140f1D嘉泰姆 | Rail-to-Rail Output,SMBusf1D嘉泰姆 ,2 Banks MTP, Checksumf1D嘉泰姆 | TQFN5X5-32f1D嘉泰姆 |

CXLC8981f1D嘉泰姆 | 7f1D嘉泰姆 | 18f1D嘉泰姆 | 1f1D嘉泰姆 | 100f1D嘉泰姆 | 23f1D嘉泰姆 | 20f1D嘉泰姆 | 270f1D嘉泰姆 | SMBus,Rail-to-Rail Outputf1D嘉泰姆 | TDFN3X3-8f1D嘉泰姆 |

CXLC8982f1D嘉泰姆 | 7f1D嘉泰姆 | 18f1D嘉泰姆 | 1f1D嘉泰姆 | 100f1D嘉泰姆 | --f1D嘉泰姆 | --f1D嘉泰姆 | --f1D嘉泰姆 | SMBus, VCOM REFf1D嘉泰姆 | TDFN3X3-8f1D嘉泰姆 |

CXLC8983f1D嘉泰姆 | 7f1D嘉泰姆 | 20f1D嘉泰姆 | 8+1f1D嘉泰姆 | 25, 100f1D嘉泰姆 | 16, 50f1D嘉泰姆 | 30f1D嘉泰姆 | 100, 300f1D嘉泰姆 | SMBus, Rail-to-Rail f1D嘉泰姆 Output,2 Bank MTPf1D嘉泰姆 | QFN4X4-24f1D嘉泰姆 |

f1D嘉泰姆

中文

中文 English

English

发表评论