# **Ultra Low Power Battery Monitor**

## 6100

### **General Description**

The JTM6100 is an ultra low power battery monitor, and is specially designed for monitoring single or multi lithium-ion (Li+) cells, multi-cell alkaline, NiCd, NiMH and multi-cell lead acid batteries. The device offers a single low-battery output and features fixed hysteresis. The hysteresis eliminates the output chatter sometimes associated with battery voltage monitors, usually due to input voltage noise or battery terminal voltage recovery after load removal.

The device is available in 5 pin SOT23 package and is fully specified over the -40  $^{\circ}$ C to +85  $^{\circ}$ C extended temperature range.

## **Applications**

- Battery-powered Systems

- Multi-cell Li+ Batteries Monitoring

- Multi-cell Alkaline, NiCd or NiMH Batteries Monitoring

- Multi-cell Lead Acid Batteries Monitoring

#### **Features**

- Precise Reset Threshold: ±2%

- Hysteresis to Eliminate the Output Chatter

- CMOS Output

- 60ms typical Delay to Filter out the noise

- 1.8 μA Supply Current @Vcc=3V

- Guaranteed Output Valid to  $V_{CC} = +1.15V$

- Power Supply Transient Immunity

- Operating Temperature Range

-40 ℃ to +85 ℃

- Available in SOT23-5

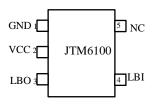

### Pin Assignment

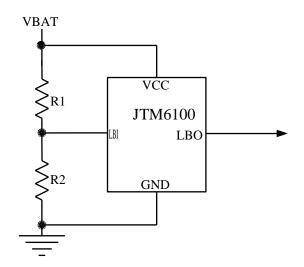

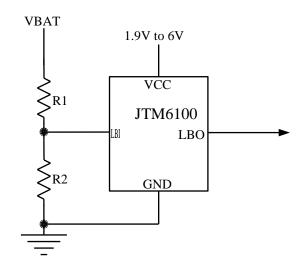

# **Typical Application Circuit**

Figure 1 Monitoring Battery Voltage Lower Than 6V

Figure 2 Monitoring Battery Voltage Higher Than 6V

# **Pin Description**

| Pin No. | Symbol | Description                                                                                                                                                                                                                                        |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND    | Negative Terminal of Power Supply(Ground)                                                                                                                                                                                                          |

| 2       | Vcc    | Positive Terminal of Power Supply. This pin is the power supply to internal circuit.                                                                                                                                                               |

| 3       | LBO    | Low Battery Output. CMOS output. If the voltage at LBI pin is higher than the rising threshold for more than 60ms typical, LBO will transition to high; If the voltage at LBI pin is lower than the falling threshold, LBO will transition to low. |

| 4       | LBI    | Low Battery Input. The voltage that needs to be monitored is sensed at this pin. Generally LBI pin should be tied to an external resistor divider to sense the battery voltage.                                                                    |

| 5       | NC     | No Connection.                                                                                                                                                                                                                                     |

### **ABSOLUTE MAXIMUM RATINGS**

| Terminal Voltage (With respect to GND) | Thermal Resistance300°C/W                                              |

|----------------------------------------|------------------------------------------------------------------------|

| Vcc0.3V to +6.5V                       | Operating Temperature40 to +85 $^{\circ}\mathrm{C}$                    |

| LBI and LBO0.3V to Vcc                 | Storage Temperature65 to +150 $^{\circ}\mathrm{C}$                     |

| Input/Output Current                   | Lead Temperature (soldering, 10s)+260 $\mbox{\ensuremath{\mathbb{C}}}$ |

| Vcc, LBI and LB20mA                    |                                                                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

(Vcc=3V, Ta=  $-40^{\circ}$ C to 85°C, Typical values are at Ta=25°C, unless otherwise noted.)

| Parameters                 | Symbol | Test Conditions                            | Min     | Тур   | Max   | Unit |

|----------------------------|--------|--------------------------------------------|---------|-------|-------|------|

| Operating Voltage<br>Range | Vcc    |                                            | 1.9     |       | 6     | V    |

| Operating Current          | Ivcc   | Vcc=3.0V                                   | 1       | 1.8   | 4     | uA   |

| Operating Current          |        | Vcc=5.0V                                   | 1       | 2.0   | 4.2   |      |

| Rising Threshold           | Vrth   | LBI pin voltage rising                     | 1.195   | 1.22  | 1.244 | V    |

| Falling Threshold          | Vfth   | LBI pin voltage falling                    |         | 1.13: | 5     | ] '  |

| LBI Pin Bias Current       | Ilbi   |                                            | -100    | 0     | 100   | nA   |

| TC of Rising Threshold     | TC     | -40°C to 85°C                              |         |       | ±100  | ppm  |

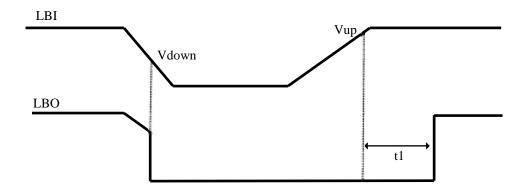

| LBI to LBO Delay           | t1     | LBI pin voltage rising                     | 30      | 60    | 100   | ms   |

| LDI to LDO Delay           | t2     | LBI pin voltage falling                    |         | 20    |       | us   |

|                            |        | Vcc=2V, Vlbi=0V                            |         |       | 0.3   |      |

|                            |        | Isink=1.5mA                                |         |       | 0.5   |      |

| LBO Low Voltage            | Vol    | Vcc=3V, Vlbi=0V                            |         |       | 0.3   | V    |

|                            |        | Isink=3.2mA                                |         |       | 0.5   |      |

|                            |        | $V_{\text{CC}}=5V, V_{\text{LBI}}=0V$      |         |       | 0.3   |      |

|                            |        | Isink=6mA                                  |         |       | 0.5   |      |

|                            | Vон    | $V_{\text{CC}}=2V$ , $V_{\text{LBI}}=1.5V$ | Vcc-0.4 |       |       |      |

|                            |        | Isource=1.5mA                              | VCC-0.4 |       |       |      |

| LBO High Voltage           |        | $V_{CC=3V}$ , $V_{LBI}=1.5V$               | Vcc-0.4 |       |       | V    |

|                            |        | Isource=3mA                                | VCC-0.4 |       |       |      |

|                            |        | $V_{\text{CC}}=5V, V_{\text{LBI}}=1.5V$    | Vcc-0.4 |       |       |      |

|                            |        | Isource=5mA                                | VCC-0.4 |       |       |      |

# **Detailed Description**

JTM6100 is an ultra low power battery monitor, if the voltage at LBI pin falls below the falling threshold, LBO will become low after a short delay(20us typical); If the voltage at LBI pin goes higher than the rising threshold, LBO will become high after a delay of 60ms typical, the delay can filter out the noise or any disturbance on the monitored voltage caused by the load switch on or switch off, so the system reliability is enhanced. The difference between rising threshold and falling threshold is also called hysteresis, which can provide noise immunity and to remove the possibility of output chatter due to battery terminal voltage recovery after the load removal.

JTM6100 is specially designed for monitoring single or multi lithium-ion (Li+) cells, multi-cell alkaline, NiCd, NiMH and multi-cell lead acid batteries.

The operation of the device can be best understood by referring to figure 3.

Figure 3 Timing waveform

### **Applications Information**

#### R1 and R2 Selection

LBI pin senses the battery voltage via the resistor divider formed by R1 and R2 in Figure 1 and Figure 2. Choosing the proper R1 and R2 values is a balance between accuracy and power consumption. The leakage current into LBI pin travels through the resistor divider and introduce an error, If extremely high resistor values are used, the leakage current introduces a significant error; While with extremely low resistor values, the error becomes negligible, but the resistive divider draws more power from the battery than necessary and shortens battery life.

The battery voltage at which LBO should activate is calculated by the following equation:

VBAT =

$$\frac{R1 + R2}{R2}$$

X Vrth + ILBI X R1

Where,

ILBI is the leakage current into LBI pin

Vrth is the rising threshold

From the above equation, if ILBI=5nA, R1=2M $\Omega$ , then the error is about 10mV

So the maximum R1 value should be decided by the acceptable error, and the minimum value should be decided by the battery power consumption due to R1 and R2's presence.

#### **Adding External Capacitance to Enhance Noise Immunity**

If monitoring voltages in a noisy environment, add a bypass capacitor of  $0.1\mu F$  from battery terminal to GND as close as possible to the device. For systems with large transients, additional capacitance may be required. A small capacitor (<1nF) from LBI pin to GND may provide additional noise immunity.

### **Negative-Going LBI Transients**

In addition to issuing a low output at LBO pin during power-up, power-down, and brownout conditions of the monitored voltage, the JTM6100 is relatively immune to short-duration negative-going LBI transients (glitches). As the magnitude of the transient increases (goes farther below the down trip point), the maximum allowable pulse width decreases. Typically, a LBI transient that goes 35mV below the down trip point and lasts 10 µs or less will not cause a low LBO output. A bypass capacitor from LBI pin to GND provides additional transient immunity.

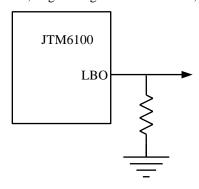

#### Ensuring a Valid LBO Down to Vcc = 0

When Vcc falls below 1.15V, JTM6100 LBO output no longer sinks current—it becomes an open circuit. Therefore, high-impedance CMOS logic inputs connected to LBO can drift to undetermined voltages. This

presents no problem in most applications, since most circuitry is inoperative with Vcc below 1.15V. However, in applications where LBO must be valid down to 0V, a pull-down resistor is needed from LBO pin to GND as shown in Figure 4, then LBO output will be held at low state. The resistor's value is not critical, it should be about  $100K\Omega$ , large enough not to load LBO, small enough to pull LBO to ground.

Figure 4 Ensuing a Valid LBO Down to VCC=0V

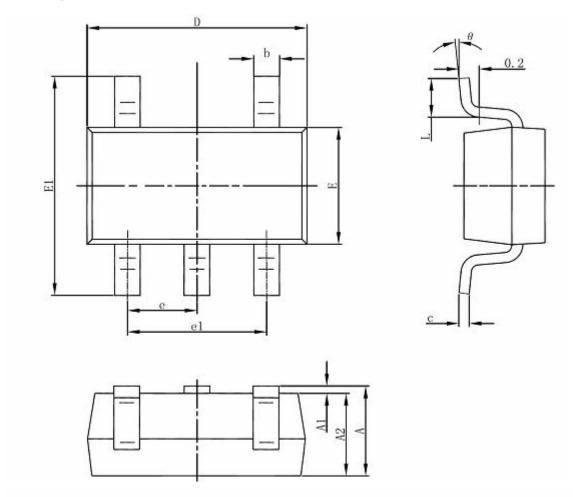

# **Package Information**

| Symbol | Dimensions In Millimeters |       | Dimensions In Inches |       |  |

|--------|---------------------------|-------|----------------------|-------|--|

|        | Min                       | Max   | Min                  | Max   |  |

| Α      | 1.050                     | 1.250 | 0.041                | 0.049 |  |

| A1     | 0.000                     | 0.100 | 0.000                | 0.004 |  |

| A2     | 1.050                     | 1.150 | 0.041                | 0.045 |  |

| b      | 0.300                     | 0.500 | 0.012                | 0.020 |  |

| С      | 0.100                     | 0.200 | 0.004                | 0.008 |  |

| D      | 2.820                     | 3.020 | 0.111                | 0.119 |  |

| E      | 1,500                     | 1.700 | 0.059                | 0.067 |  |

| E1     | 2.650                     | 2.950 | 0.104                | 0.116 |  |

| е      | 0.950(BSC)                |       | 0.037(BSC)           |       |  |

| e1     | 1.800                     | 2.000 | 0.071                | 0.079 |  |

| L      | 0.300                     | 0.600 | 0.012                | 0.024 |  |

| θ      | 0°                        | 8°    | 0°                   | 8°    |  |

Consonance does not assume any responsibility for use of any circuitry described. Consonance reserves the right to change the circuitry and specifications without notice at any time.