|

目前,处理器性能的主要衡量指标是时钟频率。绝大多数的集成电路 (IC) 设计都基于同步架构,而同步架构都采用全球一致的时钟。这种架构非常普及,许多人认为它也是数字电路设计的唯一途径。然而,有一种截然不同的设计技术即将走上前台:异步设计。

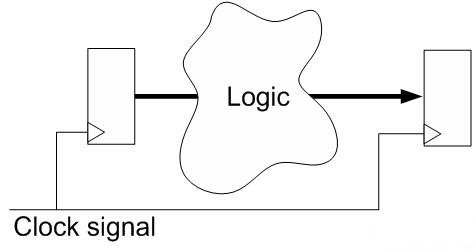

这一新技术的主要推动力来自硅技术的发展状况。随着硅产品的结构缩小到 90 纳米以内,降低功耗就已成为首要事务。异步设计具有功耗低、电路更可靠等优点,被看作是满足这一需要的途径。 异步技术由于诸多原因曾经备受冷落,其中最重要的是缺乏标准化的工具流。IC 设计团队面临着巨大的压力,包括快速地交付设备,使用高级编程语言和标准的事件驱动架构 (EDA) 工具,帮助实施合成、定时和验证等任务。如果异步设计可以使用此类工具,那么可以预计将会出现更多采用异步逻辑组件的设备。 在过去,小型异步电路仅用作同步电路的补充。仅仅在最近,新发布的商用设备才主要基于异步设计。但是此类设备主要针对小众市场,如要求超低功耗和稳定电流的嵌入式感应器。 我们正在见证一款完全基于异步逻辑的通用数字信号处理器(DSP)核心横空出世。无论是 IC 设计人员还是最终用户,它带来的好处数不胜数。 同步与异步 目前的数字设计事实上采用的是同步设计技术。由于历史原因,这种方法得到了改良,设计工具也不断演化。目前有一种标准流以高级语言为基础,可实现快速开发。同步设计还可以轻松地扩展设备性能。设计人员只须提高时钟频率,就能使设计变得更快。 同步法包括建立功能模块,每个模块由一个按时钟信号控制的有限状态机(FSM)驱动。触发器被用于存储当前状态。当接收到时钟信号时,触发器将更新所存储的值。 在 DSP 的设计过程中,逻辑阶段必不可少。这些阶段实施操作并将结果传递到下一阶段。下图表示单个阶段的简单模型。异步逻辑用于在两个触发器之间计算电路的新状态。例如,该逻辑云可执行加法或乘法。

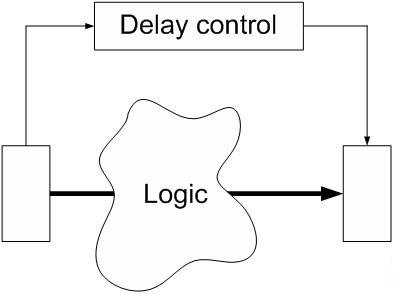

Logic 逻辑 Clock signal 时钟信号 对于异步 DSP 核心,逻辑阶段被调整以消除时钟。下图显示了这种DSP 架构的基本构造。不是由时钟控制门闩线路,而实际上是传递了一个完成信号给下一逻辑阶段。根据逻辑云所执行的操作,在恰当时候可生成完成信号。 这种本地延迟控制可以保证电路的稳定。由于控制电路时间的逻辑就在本地,它就可以相应地改变电压、处理速度和温度。

Delay control 延时控制 Logic 逻辑 异步设计有许多种不同的途径,而前提是电路不受单一时钟控制。多数情况下,异步逻辑被用于通过专门的电路设计来解决具体问题。但是,异步逻辑也可用作完 整 DSP核心的基础,而不仅仅是设计中偶尔需要的一种工具。其好处包括降低功耗、可靠性提高以及电磁干扰(EMI)低。 异步设计的好处 采用异步设计的理由非常吸引人。在正确使用中,这种方法可以实现更低的能耗、更好的EMI 性能;由于消除了全球时钟偏差,真正地简化了设计。 功耗更低:与同步DSP核心相比,异步DSP最重要的好处就是功耗更低。事实上,这种异步核心的能效数量级高于最好的同步DSP。 (责任编辑:oumao18) |