目录

产品概述 返回TOPowI嘉泰姆

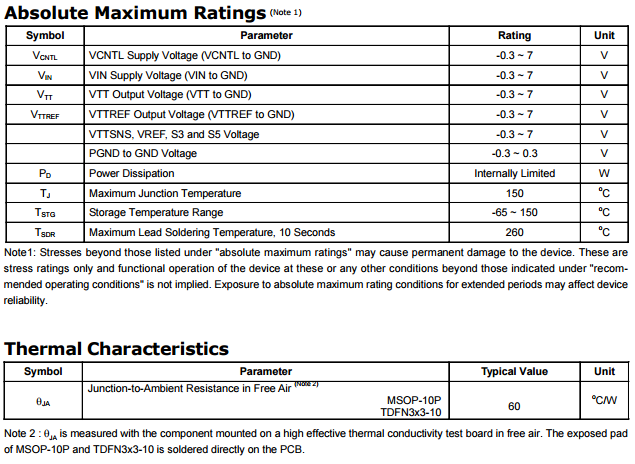

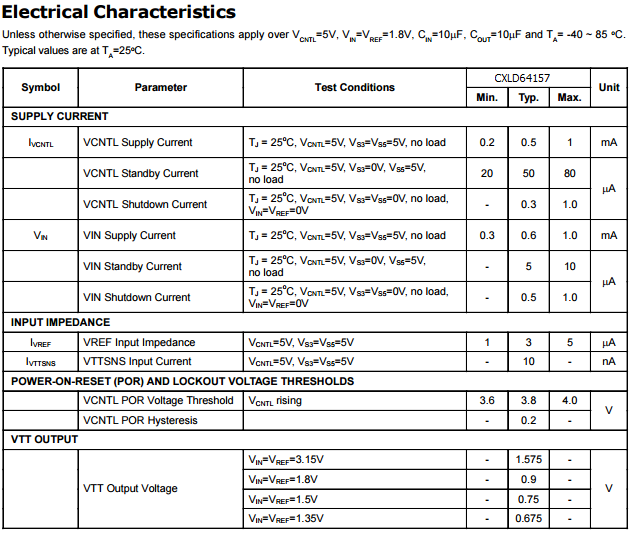

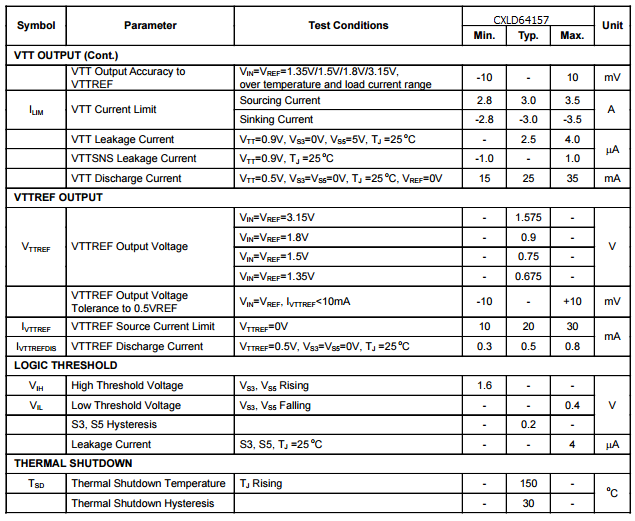

The CXLD64157 CXLD64157A linear regulator is designed to provide a

regulated voltage with bi-directional output current for

DDR-SDRAM termination. The CXLD64157 CXLD64157A integrates two

power transistors to source or sink current up to 2A. It

also incorporates current-limit and thermal shutdown into

a single chip.

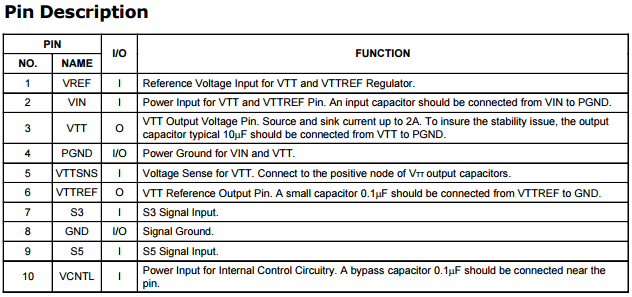

The output voltage of CXLD64157 CXLD64157A tracks the voltage at VREF

pin. An internal resistor divider is used to provide a half

voltage of VREF for VTTREF and VTT Voltage. The VTT

output voltage is only requiring 10mF of ceramic output

capacitance for stability and fast transient response. The

S3 and S5 pins provide the sleep state for VTT (S3 state)

and suspend state (S4/S5 state) for device when S5 and

S3 are both pulled low the device provides the soft-off for

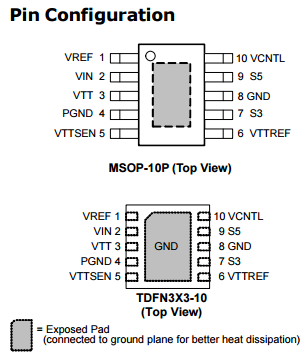

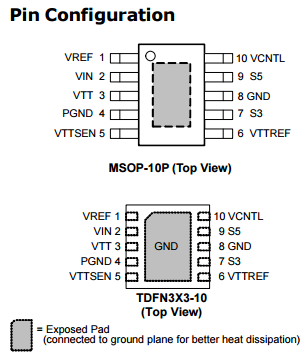

VTT and VTTREF. The MSOP-10P and TDFN3x3-10 package

with a copper pad is available which provides excellent

thermal impedance.

产品特点 返回TOPowI嘉泰姆

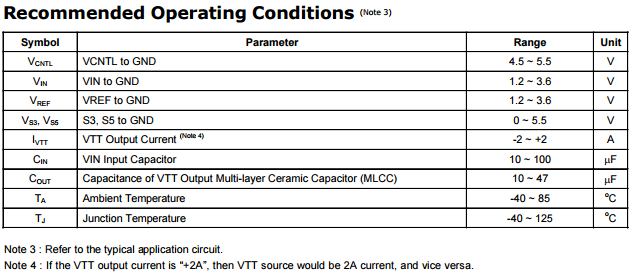

· Sourcing and Sinking Current up to 2A owI嘉泰姆

· Wide Input Voltage Range: 1.2V to 3.6V owI嘉泰姆

· VTT and VTTREF Voltage Tracks at Half the VREF

Voltage owI嘉泰姆

· VTT and VTTREF Voltage with ±10mV Accuracy owI嘉泰姆

· Excellent Load Transient Response owI嘉泰姆

· Stable with 10mF Ceramic Output Capacitor owI嘉泰姆

· Current-Limit Protection owI嘉泰姆

· Thermal Shutdown Protection owI嘉泰姆

· Power-On-Reset Function on VCNTL owI嘉泰姆

· S3, S5 Input Signals for ACPI States owI嘉泰姆

· Small MSOP-10P and TDFN3x3-10 Packages owI嘉泰姆

· Lead Free and Green Devices Available

(RoHS Compliant)owI嘉泰姆

应用范围 返回TOPowI嘉泰姆

· DDR 2/3 Memory TerminationowI嘉泰姆

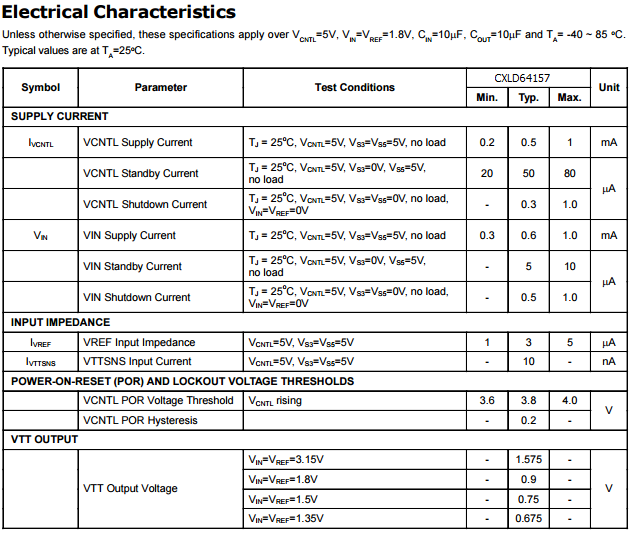

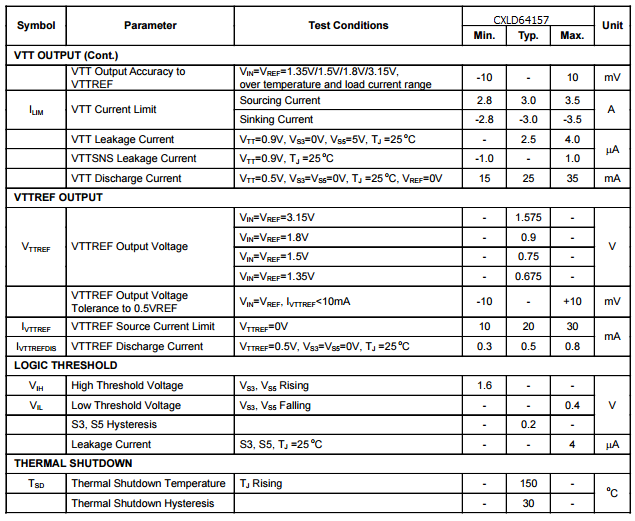

技术规格书(产品PDF) 返回TOP owI嘉泰姆

需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持</span>!</span>

owI嘉泰姆

owI嘉泰姆

owI嘉泰姆

产品封装图 返回TOPowI嘉泰姆

owI嘉泰姆

owI嘉泰姆

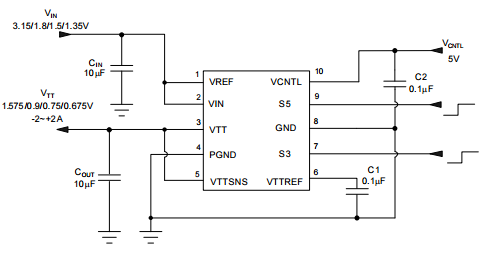

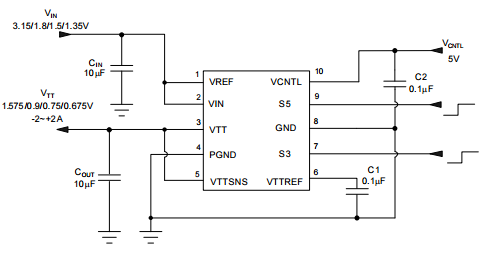

电路原理图 返回TOPowI嘉泰姆

owI嘉泰姆

owI嘉泰姆

owI嘉泰姆

Products > Linear Regulator > DDR Termination RegulatorowI嘉泰姆 |

Part_No owI嘉泰姆 | Package owI嘉泰姆 | InputowI嘉泰姆 Voltage owI嘉泰姆 (V) owI嘉泰姆 | VCNTL owI嘉泰姆 Voltage owI嘉泰姆 (V) owI嘉泰姆 | Quiescent owI嘉泰姆 Current owI嘉泰姆 (uA) owI嘉泰姆 | Output owI嘉泰姆 Sink owI嘉泰姆 Current owI嘉泰姆 (max)(A) owI嘉泰姆 | Output Source Current (max)(A) owI嘉泰姆 | DDR Power owI嘉泰姆 | VTTREF owI嘉泰姆 | S3/S5 owI嘉泰姆 |

minowI嘉泰姆 | maxowI嘉泰姆 | minowI嘉泰姆 | maxowI嘉泰姆 |

CXLD64155owI嘉泰姆 | SOP8/TO252-5/TO263-5owI嘉泰姆 | 1.2owI嘉泰姆 | 3.5owI嘉泰姆 | 3.1owI嘉泰姆 | 6owI嘉泰姆 | 3900owI嘉泰姆 | 3owI嘉泰姆 | 3owI嘉泰姆 | DDR1/DDR2/owI嘉泰姆 DDR3owI嘉泰姆 | NowI嘉泰姆 | NowI嘉泰姆 |

CXLD64156owI嘉泰姆 | MSOP-10owI嘉泰姆 | 1.2owI嘉泰姆 | 3.6owI嘉泰姆 | 4.5owI嘉泰姆 | 5.5owI嘉泰姆 | 2000owI嘉泰姆 | 3owI嘉泰姆 | 3owI嘉泰姆 | DDR1/DDR2/owI嘉泰姆 DDR3owI嘉泰姆 | YowI嘉泰姆 | YowI嘉泰姆 |

CXLD64157owI嘉泰姆 | MSOP1owI嘉泰姆 0TDFN3x3-10owI嘉泰姆 | 1.2owI嘉泰姆 | 3.6owI嘉泰姆 | 4.5owI嘉泰姆 | 5.5owI嘉泰姆 | 600owI嘉泰姆 | 2owI嘉泰姆 | 2owI嘉泰姆 | DDR2/DDR3owI嘉泰姆 | YowI嘉泰姆 | YowI嘉泰姆 |

CXLD64157AowI嘉泰姆 | MSOP1owI嘉泰姆 0TDFN3x3-10owI嘉泰姆 | 1.2owI嘉泰姆 | 3.6owI嘉泰姆 | 3.1owI嘉泰姆 | 5.5owI嘉泰姆 | 600owI嘉泰姆 | 2owI嘉泰姆 | 2owI嘉泰姆 | DDR2/DDR3owI嘉泰姆 | YowI嘉泰姆 | YowI嘉泰姆 |

CXLD64158owI嘉泰姆 | SOP-8/powI嘉泰姆 | 1.1owI嘉泰姆 | 4.5owI嘉泰姆 | 3owI嘉泰姆 | 5.5owI嘉泰姆 | 1000owI嘉泰姆 | 2owI嘉泰姆 | 2owI嘉泰姆 | DDR2/DDR3owI嘉泰姆 | NowI嘉泰姆 | NowI嘉泰姆 |

Products > Linear Regulator > LDO Regulator ControllerowI嘉泰姆 |

Part_No owI嘉泰姆 | Package owI嘉泰姆 | VCNTLowI嘉泰姆 Voltage (V) owI嘉泰姆 | QuiescentowI嘉泰姆 Current owI嘉泰姆 (uA) owI嘉泰姆 | Driver owI嘉泰姆 CurrentowI嘉泰姆 (mA) owI嘉泰姆 | Reference owI嘉泰姆 VoltageowI嘉泰姆 (V) owI嘉泰姆 | EN owI嘉泰姆 | POK owI嘉泰姆 | SS owI嘉泰姆 |

minowI嘉泰姆 | maxowI嘉泰姆 |

CXLD64159owI嘉泰姆 | SOT-23-6owI嘉泰姆 | 4.5owI嘉泰姆 | 13.5owI嘉泰姆 | 800owI嘉泰姆 | 50owI嘉泰姆 | 0.8/0.5owI嘉泰姆 | YowI嘉泰姆 | YowI嘉泰姆 | NowI嘉泰姆 |

CXLD64160owI嘉泰姆 | SOT-23-6owI嘉泰姆 | 4.5owI嘉泰姆 | 13.5owI嘉泰姆 | 800owI嘉泰姆 | 50owI嘉泰姆 | 0.8/0.5owI嘉泰姆 | YowI嘉泰姆 | NowI嘉泰姆 | YowI嘉泰姆 |

owI嘉泰姆

中文

中文 English

English

发表评论