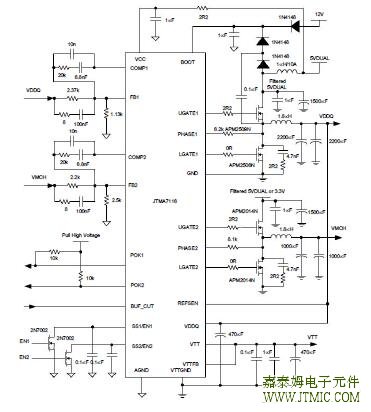

六.电路原理图

七,功能概述

Output Inductor Selection

The inductor value determines the inductor ripple current and affects the load transient response.

Higher inductor value reduces the inductor’s ripple current and induces lower output ripple voltage.

The ripple current and ripple voltage can be approximated by:where FS is the switching frequency

of the regulator.Although increases the inductor value to reduce the ripple current and voltage, there

is a tradeoff existing between the inductor’s ripple current and the regulator load tran-sient response time.

A smaller inductor will give the regulator a faster load transient response at the expense of higher ripple current.

The maximum ripple current occurs at the maximum in-put voltage. A good starting point is to choose

the ripple current to be approximately 30% of the maximum output current.Once the inductance value

has been chosen, select an inductor that is capable of carrying the required peak cur-rent without going

into saturation. In some types of inductors, especially core that is make of ferrite, the ripple current will

increase abruptly when it saturates. This will result in a larger output ripple voltage.

Output Capacitor Selection

Higher Capacitor value and lower ESR reduce the output ripple and the load transient drop. Therefore,

select high performance low ESR capacitors are intended for switch-ing regulator applications.

In some applications, mul-tiple capacitors have to be parallelled to achieve the de-sired ESR value.

A small decoupling capacitor in parallel for bypassing the noise is also recommended, and the

voltage rating of the output capacitors also must be considered. If tantalum capacitors are used,

make sure they are surge tested by the manufactures. If in doubt, consult the capacitors manufacturer.

Input Capacitor Selection

The input capacitor is chosen based on the voltage rat-ing and the RMS current rating. For reliable

operation,select the capacitor voltage rating to be at least 1.3 times higher than the maximum input voltage.

The maximum RMS current rating requirement is approximately IOUT/2,where IOUT is the load current.

During power-up, the input capacitors have to handle large amount of surge current.

If tantalum capacitors are used, make sure they are surge tested by the manufactures. If in doubt,

consult the ca- pacitors manufacturer. For high frequency decoupling, a ceramic capacitor 1µF can be

connected between the drain of upper MOSFET and the source of lower MOSFET.

MOSFET Selection

The selection of the N-channel power MOSFETs are de-termined by the RDS(ON), reverse transfer

capacitance(CRSS)and maximum output current requirement. The losses in the MOSFETs have two

components: conduction loss and transition loss. For the upper and lower MOSFET, the losses are

approximately given by the following equations:

MOSFET Selection (Cont.)

PUPPER = IOUT 2(1+ TC)(RDS(ON))D + (0.5)(IOUT)(VIN)(tSW)FS

PLOWER = IOUT 2(1+ TC)(RDS(ON))(1-D)

where IOUT is the load current

TC is the temperature dependency of RDS(ON)

FS is the switching frequency

tSW is the switching interval

D is the duty cycle

Note that both MOSFETs have conduction losses while the upper MOSFET includes an additional transition

loss.The switching internal, tSW, is the function of the reverse transfer capacitance CRSS. The (1+TC) term

is to factor in the temperature dependency of the RDS(ON) and can be extracted from the “RDS(ON) vs

Temperature” curve of the power MOSFET.

Layout Consideration

In high power switching regulator, a correct layout is im-portant to ensure proper operation of the regulator. In

general, interconnecting impedances should be mini-mized by using short and wide printed circuit traces. Sig-

nal and power grounds are to be kept separating and finally combined to use ground plane construction or

single point grounding. Figure 14 illustrates the layout,with bold lines indicating high current paths; these traces

must be short and wide. Components along the boldlines should be placed close together.

Below is a checklist for your layout:

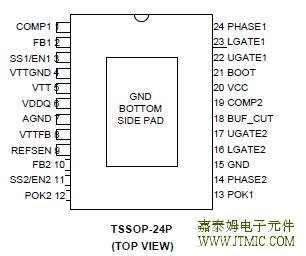

·-The metal plate of the bottom of the packages (TSSOP-24P) must be soldered to the PCB and con-nect to

the GND plane on the backside through sev-eral thermal vias. More vias is better for heatsink.

·-Keep the switching nodes (UGATE, LGATE, and PHASE) away from sensitive small signal nodes

since these nodes are fast moving signals. Therefore,keep traces to these nodes as short as possible.

· Connet the FB and VTTFB to point of load and the REFSEN should be connected to the point of load of

the VDDQ output.

· The traces from the gate drivers to the MOSFETs (UG1,LG1, UG2, and LG2) should be short and wide.

Decoupling capacitor, compensation component, the resistor dividers, boot capacitors, and SS capacitors

should be close to their pins.

The input capacitor should be near the drain of the upper MOSFET; the output capacitor should be near

the loads.

The input capacitor GND should be close to the out-put capacitor GND and the lower MOSFET GND.

The drain of the MOSFETs (VIN and phase nodes)

should be a large plane for heat sinking.

JTM3110B 是 一 款 高 效 、

人气:199

JTM3110B 是 一 款 高 效 、

人气:199