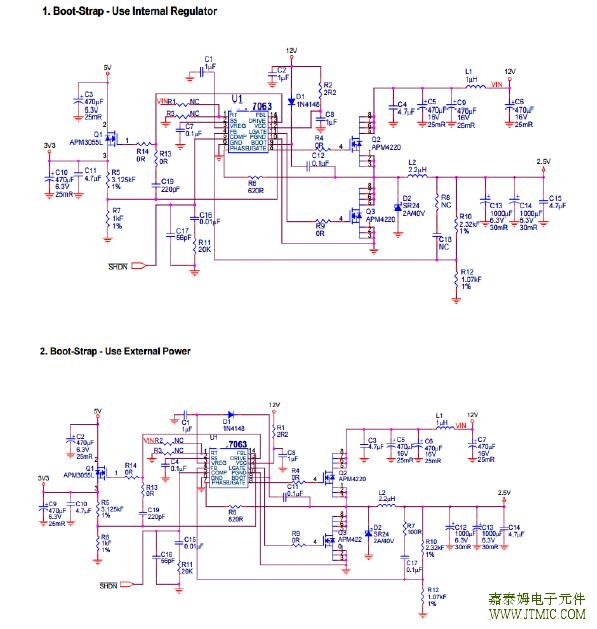

六.电路原理图

七,功能概述

MOSFET Selection

The selection of the N-channel power MOSFETs is deter-mined by the RDS(ON), reverse transfer

capacitance (CRSS),and maximum output current requirement.The losses in the MOSFETs have two

components: conduction loss and transition loss. For the upper and lower MOSFET, the losses are

approximately given by the following equations:

PUPPER = Iout (1+ TC)(RDS(ON))D + (0.5)(Iout)(VIN)(tsw)FS

where IOUT is the load current

TC is the temperature dependency of RDS(ON)

FS is the switching frequency

tsw is the switching interval

D is the duty cycle

Note that both MOSFETs have conduction losses while the upper MOSFET include an additional transition

loss.The switching internal, tsw, is the function of the reverse transfer capacitance CRSS. Figure 7 illustrates

the switch-ing waveform internal of the MOSFET.The (1+TC) term factors in the temperature dependency

of the RDS(ON) and can be extracted from the “RDS(ON) vs Tem-perature” curve of the power MOSFET.

Linear Regulator Input/Output Capacitor Selection

The input capacitor is chosen based on its voltage rating.Under load transient condition, the input capacitor will

momentarily supply the required transient current. A 1µF ceramic capacitor will be sufficient in most applications.

The output capacitor for the linear regulator is chosen to minimize any droop during load transient condition. In

addition, the capacitor is chosen based on its voltage rating.

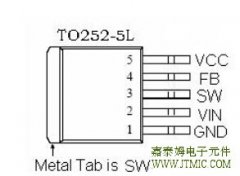

Linear Regulator MOSFET Selection

The maximum DRIVE voltage is determined by the VCC.Since this pin drives an external N-channel MOSFET, the

maximum output voltage of the linear regulator is depen-dent upon the VGS.

VOUT2MAX = VCC- VGS

Another criteria is its efficiency of heat removal. The power dissipated by the MOSFET is given by:

Pdiss = Iout * (VIN - VOUT2)

where Iout is the maximum load current

Vout2 is the nominal output voltage In some applications, heatsink may be required to help

maintain the junction temperature of the MOSFET below its maximum rating.

Layout Consideration

In high power switching regulator, a correct layout is im-portant to ensure proper operation of the regulator. In

general, interconnecting impedances should be mini-mized by using short and wide printed circuit traces. Sig-

nal and power grounds are to be kept separate and finally combined using ground plane construction or single point

grounding. Figure 8 illustrates the layout, with bold lines indicating high current paths. Components along the bold

lines should be placed close together. Below is a check-list for your layout:

· Keep the switching nodes (UGATE, LGATE, and PHASE)away from sensitive small signal nodes since these

nodes are fast moving signals. Therefore, keep traces to these nodes as short as possible.

· The ground return of CIN must return to the combine COUT (-) terminal.

JTM3110B 是 一 款 高 效 、

人气:199

JTM3110B 是 一 款 高 效 、

人气:199