1.产品概述 2.产品特点

3.应用范围 4.产品封装图

5.电路原理图 6.产品PCB

7.产品BOM 8.产品PDF文档

9.功能概述

二,产品概述(General Description)

SFL740是针对Buck架构优化的高PF值、高精度LED恒流控制器,适用于非隔离LED照明领域。该芯片采用赛威科技专利的"super- PFC/BuckTM"控制架构,能够实现高达93%的转换效率、高于0.9的功率因子、以及量产±4%的恒流精度。SFL740内置2A 600V功率管,系统成本极低。

SFL740 内置专利的高精度闭环恒流算法,支持准谐振QR和DCM模式,同时内置负载调整补偿和AC线电压补偿,大大提高了LED输出恒流精度。芯片最高工作频率被钳频在90KHz,配合输出GATE软驱动,使LED电源具有较好的传导和辐射EMI性能。

SFL740采用准谐振(QR)控制,通过谷底导通方式减少了开关损耗,显著的增加了能量转换效率。SFL740具有非常宽的VDD工作电压范围,可从10.5V到27V,使得LED系统设计更加方便。

SFL740 集成了诸多保护功能,包括VDD欠压保护,VDD 过压保护,LED短路/开路保护,芯片过温度保护,逐周期过流保护,管脚浮空保护,VDD最高电压钳位等。

SFL740提供DIP8封装形式。

三.产品特点(Features)

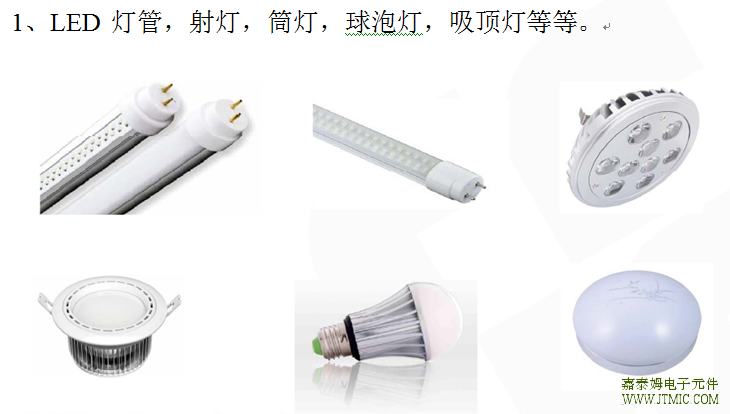

四,应用范围 (Applications)

LED lighting application

五,产品封装图 (Package)

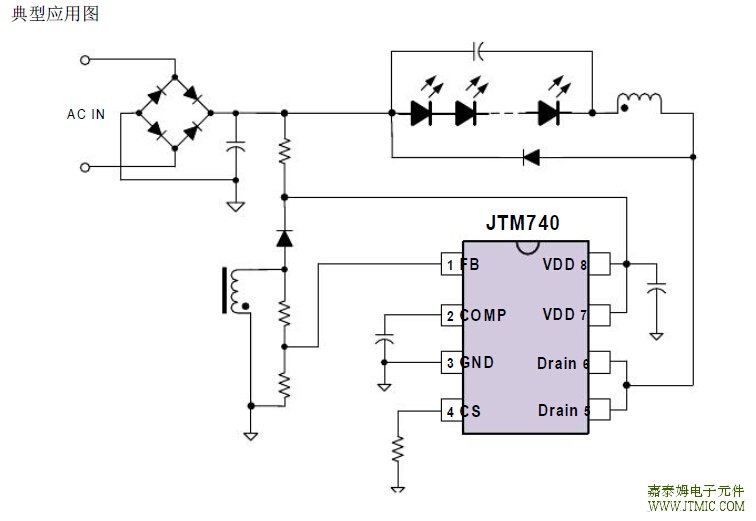

六,电路原理图

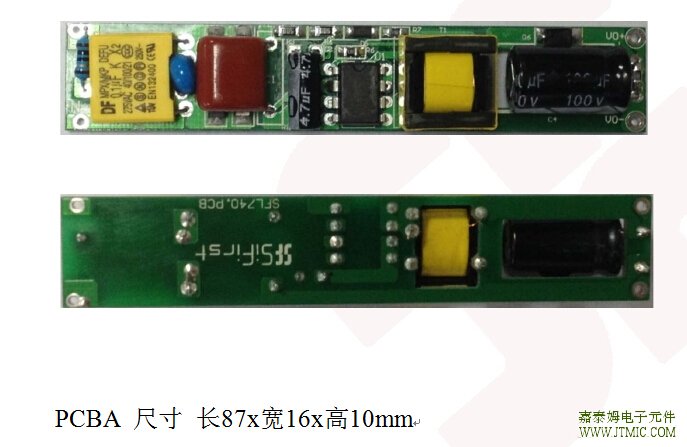

七, 产品PCB

八.产品BOM

| 序号 | 名称 | 规格 | 数量 | 位号 |

| 1 | 贴片电容 | 1uF/25V 0805 X7R 10% | 1 | C3 |

| 2 | 贴片电阻 | 1.8R 0805 1% | 1 | R1 |

| 3 | 贴片电阻 | 2.0R 0805 1% | 1 | R2 |

| 4 | 贴片电阻 | 1M 0805 5% | 2 | R3 R4 |

| 5 | 贴片电阻 | 20K 0805 5% | 1 | R5 |

| 6 | 贴片电阻 | 120K 0805 5% | 1 | R6 |

| 7 | 贴片电阻 | 2.2R 0805 5% | 1 | R7 |

| 8 | 贴片电阻 | 100K 0805 5% | 1 | R8 |

| 9 | 贴片二极管 | M7 1000V/1A SMA | 4 | D1 D2 D3 D4 |

| 10 | 贴片二极管 | A7 1000V/1A SOD123 | 1 | D5 |

| 11 | 贴片二极管 | ES1J 600V/1A SMA | 1 | D6 |

| 12 | 薄膜电容 | CAP-MPP-100nF-400V_P10 | 1 | C1 |

| 13 | 电解电容 | CAP-ELE-4.7u-50V-P2.5*Ф5*L10 | 1 | C2 |

| 14 | 电解电容 | CAP-ELE-100u-100V-P5*Ф10*L17 | 1 | C4 |

| 15 | 保险电阻 | RES-1R-1/4W | 1 | F1 |

| 16 | 压敏电阻 | VAR-Φ7-470V-07D471K | 1 | VAR1 |

| 17 | 安规电容 | CAP-X2-100nF-275VAC_P10 | 1 | CX1 |

| 18 | BUCK电感 | T1-EPC13/0.7mH(202:44T) | 1 | T1 |

| 19 | 芯片 | IC-SiFirst-SFL740-DIP8 | 1 | U1 |

| 20 | PCB | PCB-FR4/2-87mm*16.0mm*1.6mm | 1 | SFL740 |

九.产品PDF文档

|

SFL740 |

PCB Layout 注意事项

1、PCB Layout时地线尽可能短,IC的地和功率回路地分开接输入地。

2、BUCK级控制电路上所有的地先连起来然后一起连入输入滤波电容的地

。

3、VDD 脚的电容要尽量靠近VDD脚,得到好的去耦效果。

4、VDD电压建议满载时设计在16V-18V,最高不超过20V。

一个低成本、高恒流精度

人气:193

一个低成本、高恒流精度

人气:193

SFL980 单芯片集成 700V高压

人气:100

SFL980 单芯片集成 700V高压

人气:100

SFL850 PFC级还内置专利的"

人气:92

SFL850 PFC级还内置专利的"

人气:92

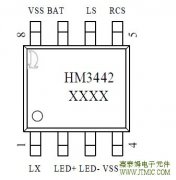

HM3442 是一款升降压型 LE

人气:57

HM3442 是一款升降压型 LE

人气:57