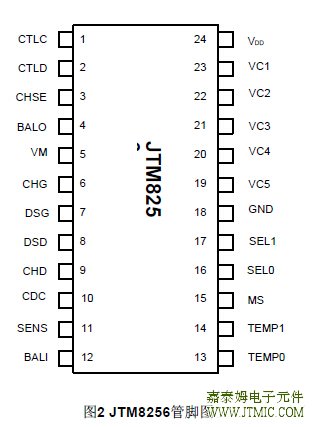

五,产品封装图 (Package)

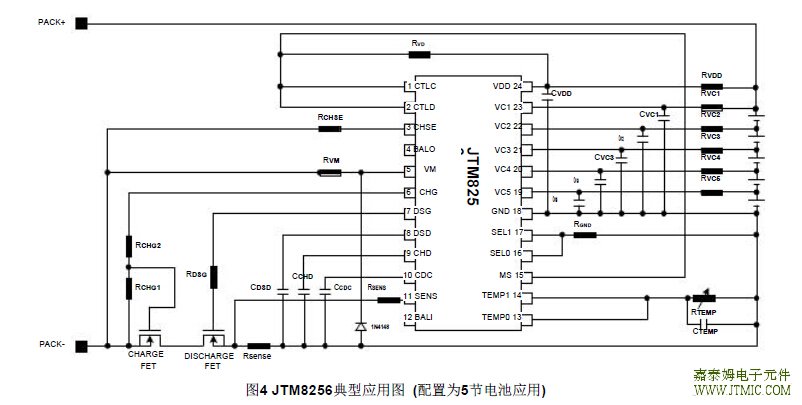

六.电路原理图

七,功能概述

1. 正常工作状态

下列条件均满足时,JTM8256 处于正常工作状态:

(1) 所有电芯电压均在过充电保护阈值电压 (VCV) 和过放电保护阈值电压 (VDV) 之间

(2) SENS 管脚上电压高于充电过流 1 保护阈值电压 (VCC1) 和充电过流 2 保护阈值电压 (VCC2),同时低于放电过流 1 保

护阈值电压 (VDC1) 和放电过流 2 保护阈值电压 (VDC2)

(3) 系统温度位于高温保护阈值温度(TH)和低温保护阈值温度(TL)之间

(4) 无平衡发生

(5) 充放电 MOS 管处于开启状态

2. 过充电状态

当任意节电芯电压超过过充电检测电压 (VCV),且此状态持续时间超过过充电检测延时 (tCD),JTM8256 系列芯片的

CHG 管脚输出高阻抗,此时 CHG 管脚会被外部电阻下拉到 PACK-从而关闭充电 MOS 管。上述状态被称之为过充电状态。

JTM8256 作为主控芯片使用时,下述任意条件满足时,过充电状态被解除:

(1) 当 JTM8256 的 CHSE 管脚电压小于 VCHSE-M (未连接负载放电),同时触发过充电保护的电芯电压小于过充电恢复

电压 (VCRV)

(2) 当 JTM8256 的 CHSE 管脚电压大于 VCHSE-M (连接负载放电),同时所有电芯电压小于过充电检测电压 (VCV);

JTM8256 作为辅控芯片使用时,下述任意条件满足时,过充电状态被解除:

a. 触发过充电保护的电芯电压小于过充电恢复电压 (VCRV)

b. 当 JTM8256 的 CHSE 管脚输入为低电平 (连接负载放电),同时所有电芯电压小于过充电检测电压 (VCV)

3. 过放电状态

当任意节电芯电压小于过放电检测电压 (VDV),且此状态持续时间超过过放电检测延时 (tDD),JTM8256 系列芯片的

DSG 管脚输出 GND 电平从而关闭放电 MOS 管。上述状态被称之为过放电状态。

JTM8256作为主控芯片使用时,下述任意条件满足时,过放电状态被解除 (系统未进入低功耗状态):

(1) JTM8256 的 CHSE 管脚电压高于 GND (未连接充电器充电),同时触发过放电保护的电芯电压高于过放电恢复电

压 (VDRV)

(2) JTM8256 的 CHSE 管脚电压小于 GND 且 CHG 管脚输出高电平 (连接充电器充电,且有充电电流),同时所有电芯

电压高于过放电检测电压(VDV);

JTM8256 作为辅控芯片使用时,下述任意条件满足时,过放电状态被解除 (系统未进入低功耗状态):

(1) 触发过放电保护的电芯电压大于过放电恢复电压 (VDRV)

(2) 当JTM8256的BALI管脚输入为低电平 (连接充电器充电,且有充电电流),同时所有电芯电压高于过放电检测电压

(VDV)

4. 低功耗状态 (可选)

JTM8256 作为主控芯片使用时,当系统进入过放电保护状态后,JTM8256 的 VM 管脚会被内部电阻 RVMD 上拉至 VDD 电

平。在上述情况下,若过放电保护状态持续时间超过 tPD,且 VM 管脚以及 CHSE 管脚电平高于 VDD/5 电平,JTM8256 系列

芯片将关闭绝大部分内部电路,从而使自身功耗减小至 IPD。上述状态被称之为低功耗状态。主控芯片进入低功耗状态

后,CHG 管脚输出高阻抗,DSG 管脚输出 GND 电平。

JTM8256 作为辅控芯片使用时,当系统进入过放电保护状态后,若过放电保护状态持续时间超过 tPD 且 JTM8256 的

BALI 管脚为高电平,JTM8256 系列芯片将关闭绝大部分内部电路,从而使自身功耗减小至 IPD。上述状态被称之为低功耗

状态。辅控芯片进入低功耗状态 6 后,CHG 管脚输出 VDD 电平,DSG 管脚输出 GND 电平。

JTM8256 作为主控芯片时,下述任意条件满足时低功耗状态被解除:

(1) VM 管脚电平小于 VDD/5

(2) CHSE 管脚电平小于 VDD/5

JTM8256 作为辅控芯片时,满足下述条件时低功耗状态被解除: (1) BALI 管脚输入电平为低电平 注释 (责任编辑:oumao18)